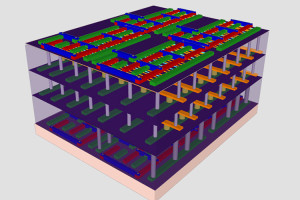

Stanford engineers have created a four-layer prototype high-rise chip. The bottom and top layers are transistors, which are sandwiched between two layers of memory.

Credit: Max Shulaker, Stanford

Cheaper, smaller, and faster – those are the three words we’re constantly hearing when it comes to innovation and development in electronics. Now, Stanford University engineers are adding a fourth word to that mantra – taller.

The Stanford team is about to reveal how to build a high-rise chip that could vault the performance of the single-story logic and memory chips on today’s circuit cards – thereby preventing the wires connecting logic and memory from jamming.

This from Stanford University:

The Stanford approach would end these jams by building layers of logic atop layers of memory to create a tightly interconnected high-rise chip. Many thousands of nanoscale electronic “elevators” would move data between the layers much faster, using less electricity, than the bottleneck-prone wires connecting single-story logic and memory chips today.