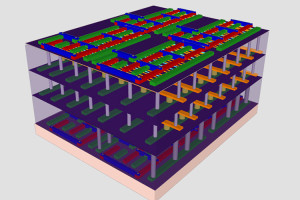

Tired of your electronics running out of memory? Rice University’s James Tour and his group of researchers have developed a solid state memory technology that allows for high-density storage while requiring 100 times less energy than traditional designs to operate.

The memory technology has been developed via tantalum oxide, a common insulator in electronics.

This from Futurity:

The discovery by the Rice University lab of chemist James Tour could allow for crossbar array memories that store up to 162 gigabits, much higher than other oxide-based memory systems under investigation by scientists. (Eight bits equal one byte; a 162-gigabit unit would store about 20 gigabytes of information.)

James Tour—a past ECS lecturer and pioneer in molecular electronics— and his group at Rice University’s Smalley Institute of Nanoscale Science & Technology are constantly demonstrating the interdisciplinary nature of nano science, and this is no exception. From the development of flexible supercapacitors to using cobalt films for clean fuel production, Tour and his lab are exploring many practical applications where chemistry and nano science intersect.